The following is the VHDL code for 4-bit SIPO in behavioural modelling. Following is the VHDL code for an 8-bit shift-left register with a positive-edge clock, serial in, and serial out. Library ieee; use ieee.std_logic_1164.all; entity shift is.

Hi guys this is my first post. In my programme i have to Design a Serial In, Parallel Out, (SIPO) sift register with a Clock and Data input (both single lines and an 8-bit parallel output Q. Serial data is accepted at the shift register input on a rising clock edge and is placed in the least significant bit – the other 7 bits of existing data shift to left. The most significant data bit is discarded once each new bit is accepted. Im having a bit of trouble with the code to discard the most significant bit. Any help will be greatly appreciated thanks Here is my code so far.

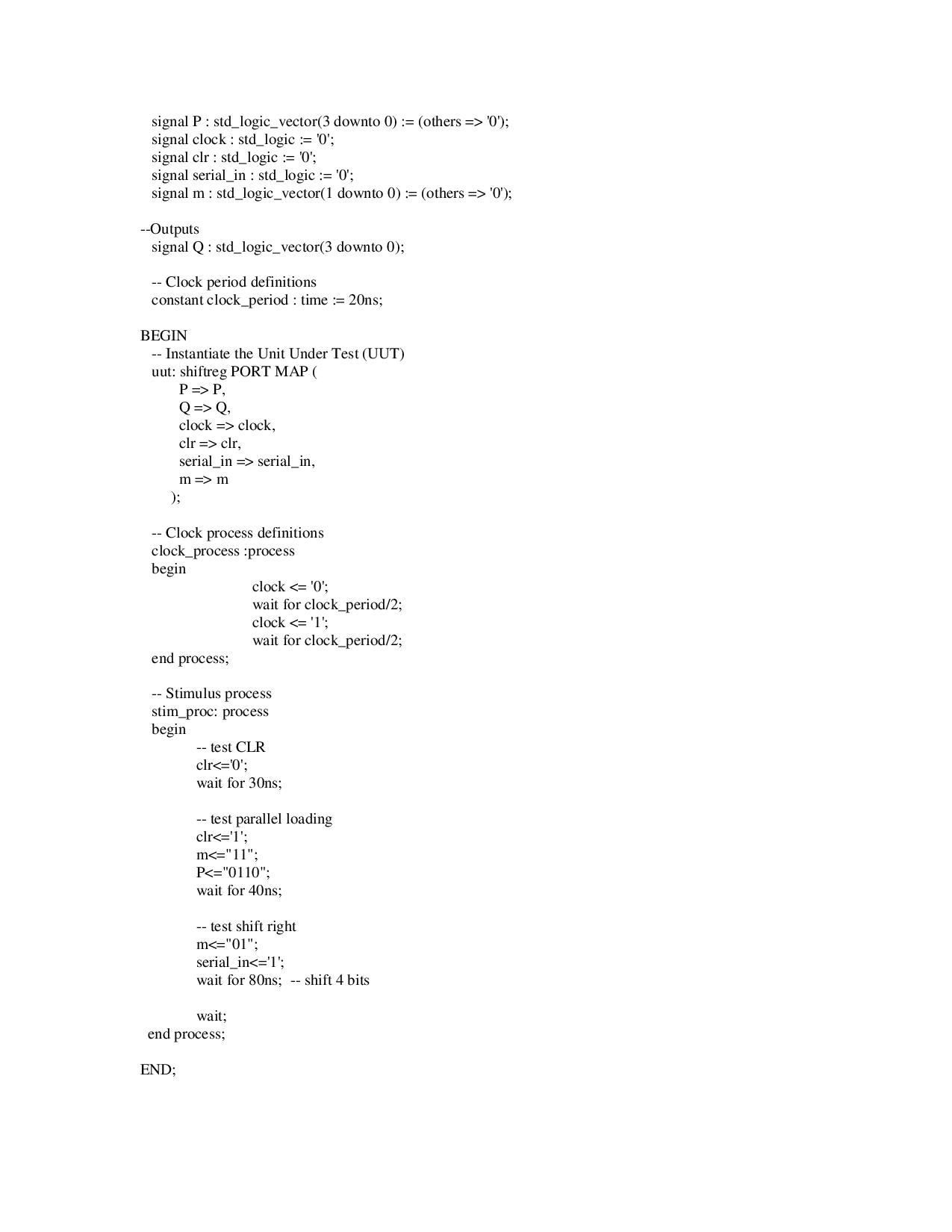

Code: - -SIMPLE GENERATE AND COMPONENT - library IEEE; use IEEE.STDLOGIC1164.ALL; use IEEE.STDLOGICARITH.ALL; use IEEE.STDLOGICUNSIGNED.ALL; entity SIPO is Generic(N:integer:=8); port(sin,clk:in STDLOGIC; sout: out STDLOGIC ); end SIPO; architecture SHIFT of SIPO is component dflipflop is port(D,clk:in STDLOGIC; Q,nQ: out STDLOGIC); end component dflipflop; signal Z: stdlogicvector (N downto 0); begin z(0). First of all, you don't need to 'discard' the MSB; when you shift D7 to Q7, the old Q7 just 'disappears'.

But a bigger problem for you is that you've used 'positional mapping', which is a sure-fire way to shoot yourself in the foot. I STRONGLY advise you to use 'nominal mapping' (e.g., clk= clk)which might take a little more effort but will avoid errors like you have (You've mapped clk to D and vice versa in your code when I THINK what you want is to map Q(z-1) to D). Another error you've got is you've generated an 8-bit register, but you're assign a 9th bit, z(8) to sout, and z(8) never gets a value. Maybe you want sout. Code: - -SIMPLE GENERATE AND COMPONENT - library IEEE; use IEEE.STDLOGIC1164.ALL; use IEEE.STDLOGICARITH.ALL; use IEEE.STDLOGICUNSIGNED.ALL; entity SIPO is Generic(N:integer:=8); port(sin,clk:in STDLOGIC; sout: out STDLOGIC ); end SIPO; architecture SHIFT of SIPO is component dflipflop is port(clk,D:in STDLOGIC; Q,nQ: out STDLOGIC); end component dflipflop; signal Z: stdlogicvector (N downto 0); begin z(0).

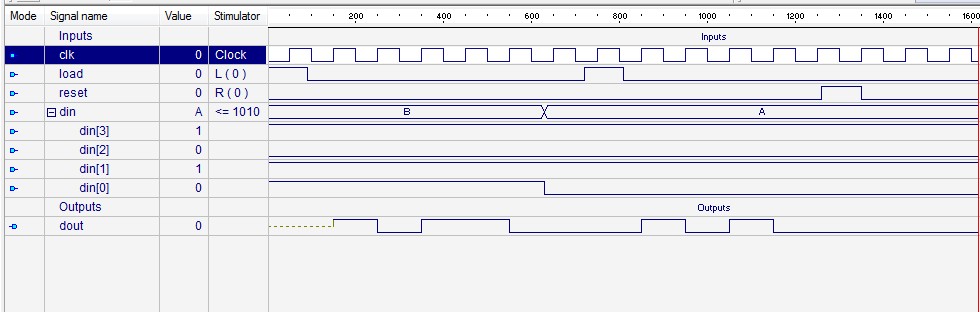

I'm creating an n bit shift register. When the enable signal is high, I want the shift register to shift n times, irrespective of whether enable continues to be high or low. I've put a for loop to shift n times inside a process. My code is given below.

I don't think the for loop is working, as the shifting is not restricted to n times. Where am I going wrong? Library ieee; use ieee.stdlogic1164.all; entity SReg is generic ( n: integer:= 4 ); port( clk: in stdlogic; reset: in stdlogic; enable: in stdlogic; -enables shifting parallelin: in stdlogicvector(n-1 downto 0); sin: in stdlogic; -serial input sout: out stdlogic -serial output ); end SReg; architecture behavioral of SReg is signal tempreg: stdlogicvector(n-1 downto 0):= (Others = '0'); begin process (clk,reset) begin if (reset = '1') then tempreg. In VHDL, a for loop executes in zero time. This means that instead of waiting a clock cycle between each iteration, the entire loop is run within one clock cycle, with only the final result of the loop being shown at the end. This is what's happening in your code.

The entire loop is executing in a single clock cycle, and the value of sout is only going to change once - to the value it was when the loop ended, which in this case is sin shifted by 4. What you really want is a loop where each iteration occurs on a new clock edge. This allows for sin to be shifted out of sout ever clock cycle. Performing a loop where each iteration occurs on a clock edge does not require a for loop command, instead it takes advantage of the sensitivity list of the process. Here's how: A process is triggered every time one of the signals on the sensitivity list ('clk, reset' in this case) changes. This means that the process is already looping every clock cycle (if a clock is in the sensitivity list). You can use this to your advantage in order to perform a for-loop type operation, where every iteration of the loop occurs on a clock cycle.

First you need a counter: process(clk,reset) variable shiftcounter: integer:= 0; begin shiftcounter keeps track of how many iterations (or shifts) have occurred so far. You'll compare shiftcounter to n-1 to see if you're done yet. Next it might be a good idea to think of the states your process will be in. Perhaps a wait state for when the process is not shifting, and a shifting state for when it is. The state signal definition: TYPE POSSIBLESTATES IS (waiting, shifting); signal state: POSSIBLESTATES; In the process proper: case state is when waiting = Ok, so what happens when we're waiting for an enable?

It would be a good idea to set all (driven) variables to a known value. This means that maybe something like this is a good idea: shiftcounter:= 0; tempreg shiftcounter:= shiftcounter + 1; sout = n-1) then state '0'); TYPE POSSIBLESTATES IS (waiting, shifting); signal state: POSSIBLESTATES; begin process(clk,reset) variable shiftcounter: integer:= 0; begin if(reset = '1') then tempreg '0'); state shiftcounter:= 0; tempreg shiftcounter:= shiftcounter + 1; sout = n-1) then state. @stanri's answer is impresively thorough and quite accurate. If I may summarize/clarify the first statement though, the 'for' statement in an HDL simply expresses 'syntactic replication' not 'sequential execution'. That is to say, it simply generates more hardware elements (gates), and does not inform process flow. I would say the loop is expanded at elaboration time (compilation), not that it 'executes in zero time', after all at runtime there will still be propagation delay through the elements generated by the 'for' construct. Don't start by writing VHDL code, start by drawing logic schematics (at least at some level of abstraction).

At the end of the day HDL is just a text-based way of expressing the content of logic schematics.